sdram model plus,SDRAM仿真模型,可用于SDRAM仿真实现。 parameter tAC = 6.5; //test 6.5 parameter tHZ = 5.5; parameter tOH = 2; parameter tMRD = 2.0; // 2 Clk Cycles parameter tRAS = 48.0; ...

”SDRAM 仿真模型 FPGA 读写测试“ 的搜索结果

接下来,结合仿真模型(镁光官网提供的 SDRAM 模型)sdr文件,和编写的 testbench 文件验证所设计的控制器是否正确。 testbench如下 `timescale 1ns/1ns `define CLK100_PERIOD 10 module sdram_control_tb; `...

FPGA驱动SDRAM

标签: fpga开发

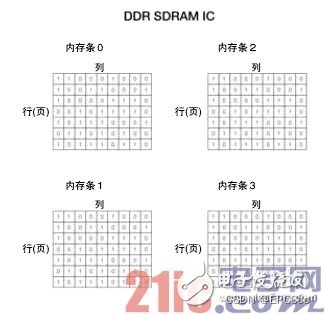

SDRAM(同步动态随机存取存储器)。

概述 本人第一次接触FPGA的设计与开发,在老师的指导下完成EP3C25Q240的实验,耗时大概3个月,两个月从零开始做实验板,一个月调试板子上的SSRAM,虽然参考了altera的EP3C25F324开发板原理图,但是自己做这样一个...

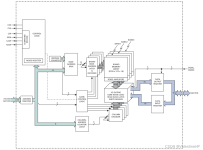

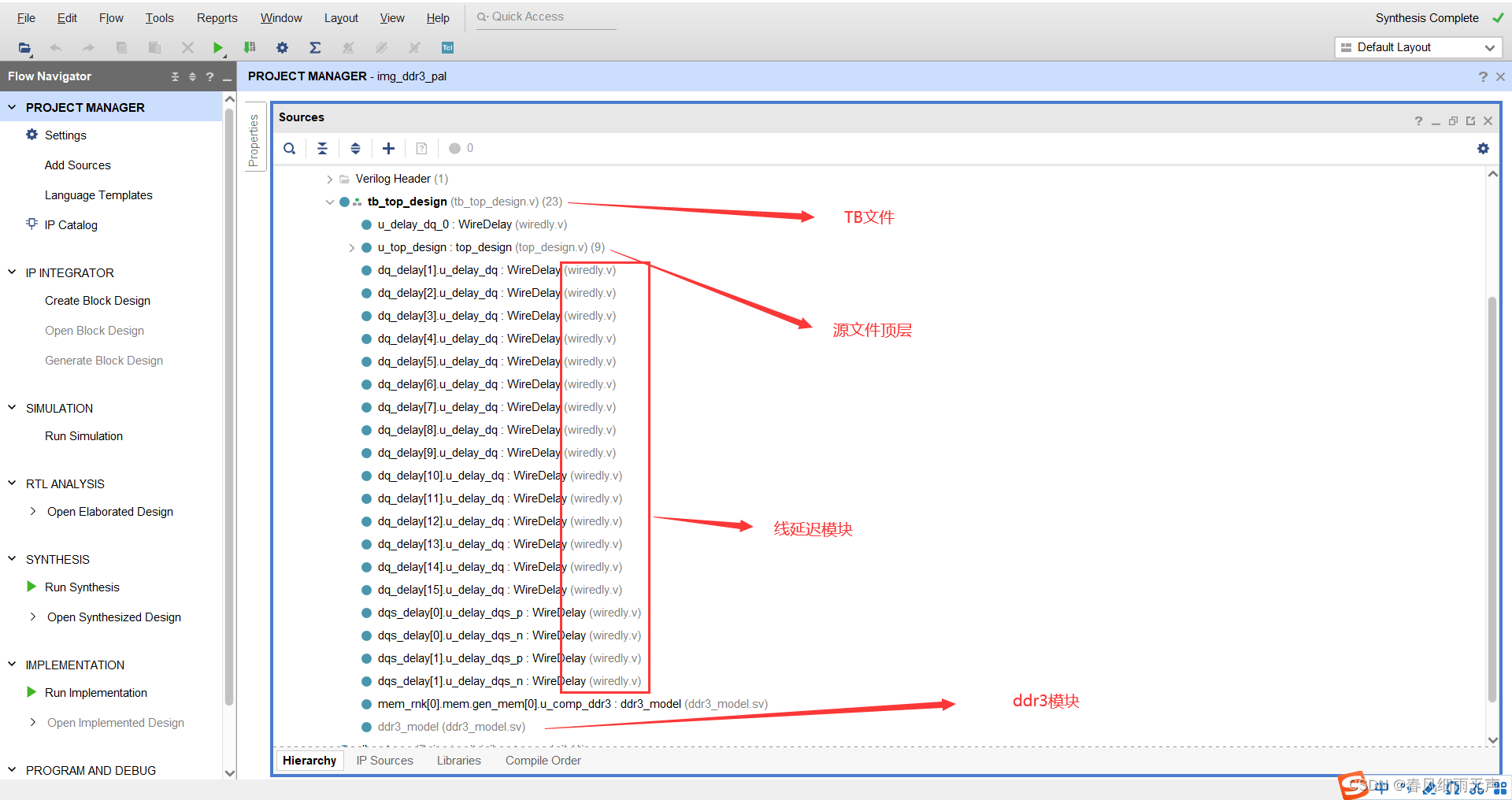

本期将接收如何驱动DDR3存储器,当然不会像SDRAM那样,自己手写驱动;而是借助Vivado提供的MIG IP来完成这项工作。但是建议在学习DDR3之前,可以学习一下且写一下SDRAM的驱动,因为它们的涉及到的存储原理和框架一样...

基于SDRAM的串口回环测试

标签: fpga开发

基于SDRAM的串口回环测试

由于直接对 DDR3 进行控制很复杂,因此一般使用 MIG IP 来实现,同时为了更...下面首先介绍 MIG IP 的配置,然后看看官方 demo (里面包含一个仿真要用到的 DDR3 模型)及其仿真结果,最后进行我们自己的控制代码实现。

RAM: 随机访问存储器,可读也可写,断电不保存数据,常用的RAM有ddr3、SDRAM。ROM仅支持读,不可写,但断电可以保存数据。随着技术的发展出现了EEPROM,它既可以断电之后保存数据也可以对数据进行改写(即可读可写...

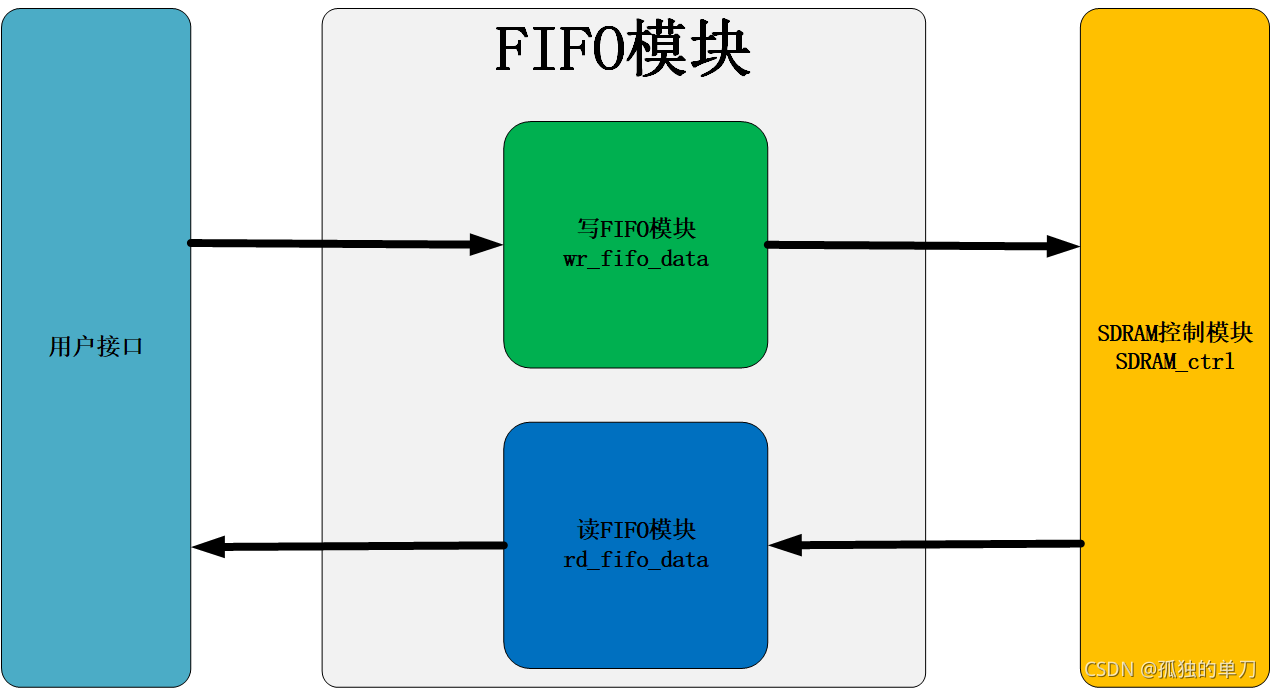

在视频图像的处理系统中,经常使用 SDRAM 作为视频图像数据的缓存。而视频图像数据流一般都是顺序产生的,同时在输出时,也只需要顺序输出即可。 对于这种连续的数据流缓存,只用上面设计的 SDRAM 控制器模块存在...

基于FPGA的SDRAM初始化配置SDRAM简述SDRAM的引脚及作用SDRAM初始化时序控制 SDRAM简述 SDRAM( Synchronous Dynamic Random Access Memory),同步动态随机存储器。同步是指 Memory 工作需要同步时钟,内部的命令的...

2、利用镁光提供的SDRAM VERILOG仿真模型进行测试 3、注意细枝末节的延时,特别是全页读写数据一定要对齐,采用全页突发+突发终止+预充电完成一次读写 4、读和写分别加上一个FIFO进行封装,为视频采集提供便利 5、...

上面是它的管脚图,关于sdram的原理网上有很多,主要要记住和理解几个重要的管脚:(1)SDRAM的CLK时钟信号,对于SDRAM芯片而言,它内部需要一个时钟,这个时钟是我们FPGA给它的,而这个时钟应该正好与FPGA内部逻辑...

上一篇文章:LiteDram仿真验证(一):安装、配置及导出Verilog,上一篇文章,在搭建好环境,导出Litedram_core.v文件后,原本计划是使用镁光的DDR3模型在Vivado或Modelsim上对这个内核进行仿真。 但是,用AXI接到...

推荐文章

- javafx预览PDF_javafx pdf-程序员宅基地

- ipv4与ipv6访问_纯ipv4访问纯ipv6-程序员宅基地

- css强制换行-程序员宅基地

- 链霉亲和素修饰的CdSe–ZnS量子点-程序员宅基地

- 饿了么4年 + 阿里2年:研发路上的一些总结与思考-程序员宅基地

- vue的sync语法糖的使用(组件父子传值)_sync传值-程序员宅基地

- 最大流最小割_网络最大流量与割的容量的关系-程序员宅基地

- queryString模块_querystring模块安装-程序员宅基地

- 安卓电量检测工具Battery Historian的使用记录_battery-historian 电量测试-程序员宅基地

- 基于QPSK的载波同步和定时同步性能仿真,包括Costas环的gardner环_qpsk符号同步-程序员宅基地